はじめに

今さらですが、ZYBO(ZYNQ-7020 Development Board)を購入したので動かしてみました。

ZYBOはDIGILENTが出しているXILINXのSOCボードです。ZYBOを選んだのは、他のSOCボードに比べて安いというシンプルな理由です。

DIGILNETのWebサイトで購入しました。

秋月電子でも販売しているようです。

動作環境

- Vivado v2020.2

- Xilinx Vitis IDE v2020.2.0

- Windows10

VIVADOを起動

既にインストールしてあるVivado v2020.2を起動してFile - Project - New。

Nextをクリック。

適当にProject Nameを入力してNextをクリック。

Nextをクリック。

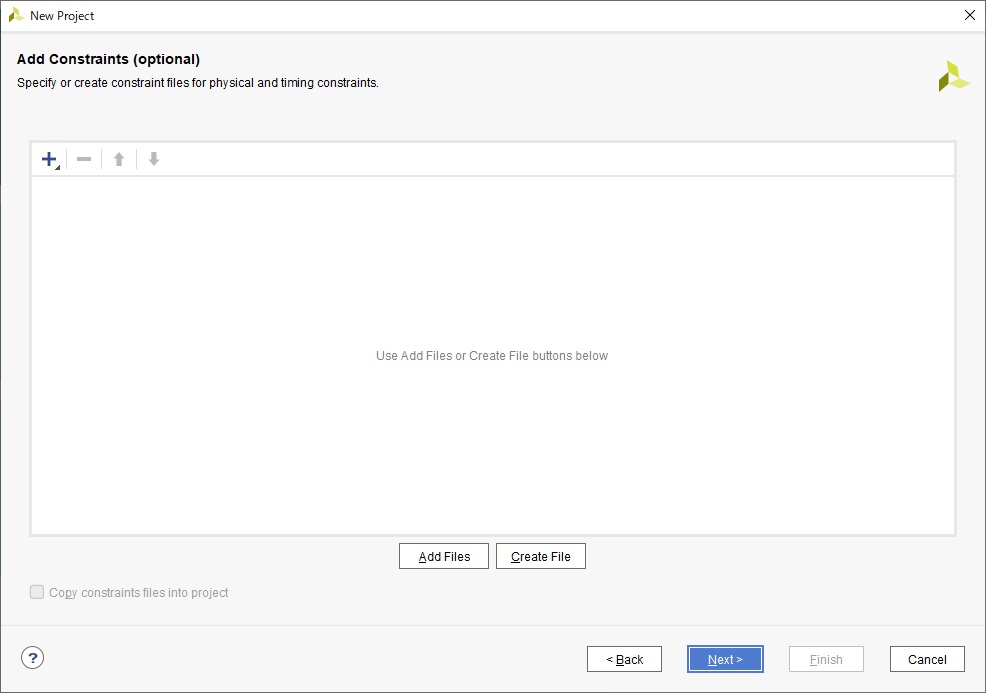

Nextをクリック。

Nextをクリック。

Boardsをクリック。

Zybo Z7-20を選択してNextをクリック。これはZYBOの初期設定の情報です。もしない場合にはDigilentの

で入手し、VIVADO2020.2の場合なら、Xilinx\Vivado\2020.2\data\boards\board_filesの下に置いた後、立ち上げなおしてください。

Finishをクリック。

VIVADOで上のような画面になります。ここで左のFlow NavigatorのCreate Block Designをクリック。

Design nameはディフォルトのdesign_1のままでOKをクリック。

Add IP (+マーク)をクリック。

ZYNQ7 Processing Systemを選びリターン。

Run Block Automationをクリック。

OKをクリック。これによりZYBOのボードの初期設定が行われます。

周辺のDDRや他のIOとの接続がされました。このIPをダブルクリックして概要を確認します。

Peripheral I/O Pinsをクリックしてみます。

どのような周辺デバイスに接続されているか確認できます。

Input Frequencyは33.333333MHzとなっています。またFCLK_CLKは50MHzとなっています。このFCLK_CLKをZYNQ7 Processing SystemのM_AXI_GP0_ACLKに供給します。

FCLK_CLK0のピンのあたりでマウスの左ボタンでドラグし、M_AXI_GP0_ACLKのピンに接続します。

File - Save Block DesignをクリックしてBlock Designを保存します。

Sourcesを選択してdesign_1の上で右クリックし、Generate Output Productsをクリック。

Generateをクリック。その後同様にdesign_1の上で右クリックし、Create HDL Wrapperをクリック。

OKをクリック。Wrapperが生成されます。

Generate Bitstreamをクリック。

Yesをクリック。

OKをクリック。これで書き込みファイルが生成されます。多少時間がかかります。

これはCancelでもかまいませんが、せっかくなのでOKをクリック。

ここでは信号のピンアサインなどが確認できます。よかったら時間のあるときに、いろいろとクリックして開いてみてください。

File - Export - Export Hardwareをクリック。

Nextをクリック。

Include bitstreamを選択してNextをクリック。

Nextをクリック。

Finishをクリック。これで実行ファイルが生成されました。

VITISを起動

Tools - Launch Vitis IDEをクリック。

今のプロジェクトの下にvitisというディレクトリをworksaceと設定してLaunchをクリック (別にどこでもいいです)。

VITISが起動しました。